- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT82V3358EDG (IDT, Integrated Device Technology Inc)IC PLL WAN SYNC ETHERNET 64TQFP

IDT82V3358

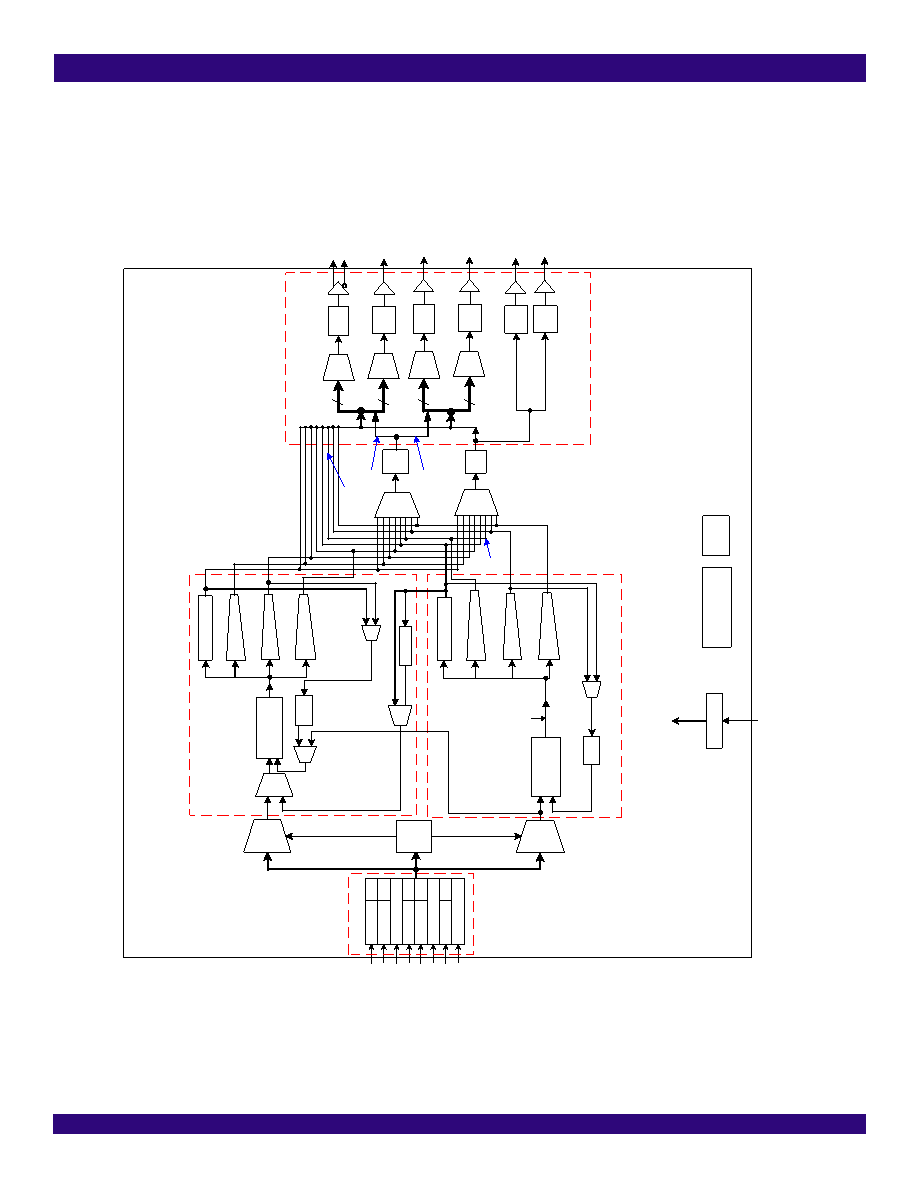

SYNCHRONOUS ETHERNET WAN PLL

Functional Block Diagram

11

May 19, 2009

FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

EX

_S

YNC

3

Mo

nitors

T0

P

FD

&L

PF

Div

ide

r

T4

P

FD

&L

PF

Div

ide

r

AP

LL

M

icr

op

ro

ce

sso

r

In

te

rface

JT

AG

PBO

Ph

as

eO

ffs

et

77

.7

6MH

z

T4

APL

L

T0

APL

L

Di

vi

de

r

OUT

1_P

O

S

OU

T7

MU

X

OUT

2

OU

T3

MU

X

MU

X

T4

APL

L

MUX

T0

APL

L

MU

X

T4

In

pu

t

Se

le

ct

or

T0

Inp

ut

Se

le

ct

or

OSCI

77

.7

6MHz

16

E1

/16

T1

12

E1

/24

T1/E

3/T3

16

E1

/16

T1

12

E1

/2

4T

1/

E3

/T

3

Au

to

Di

vi

de

r

Au

to

Di

vi

de

r

10

T0

DP

LL

T4

D

PLL

In

pu

t

IN

1_

C

M

O

S

IN

1_

D

IF

F

EX_

SYNC

1

IN2_CMO

S

IN2_DIF

F

EX_

SYNC

2

IN3_C

M

O

S

FR

SY

NC_8K

MFR

SYNC

_2

K

O

utput

G

SM

/G

PS

/16E

1/

16

T1

T

077.76

MHz

T0

8

kHz

ET

H

/O

BSA

I/1

6E

1/

16

T1

8k

Di

vi

de

r

Inp

ut

Pre

-D

iv

ide

r

Pri

ori

ty

Inp

ut

Pre

-D

iv

ide

r

Pri

ori

ty

Inp

ut

Pre

-D

iv

ide

r

Pri

ori

ty

Inp

ut

Pre

-D

iv

ide

r

Pri

ori

ty

Inp

ut

Pre

-D

iv

ide

r

Pri

ori

ty

D

iv

ider

EX

_S

YN

C

1

EX

_S

YN

C

2

EX

_S

YN

C

3

16E

1/16T

1/O

B

S

A

I

16E

1/16T

1/

O

B

S

A

I

O

U

T1_NEG

N

ote

:C

onfi

gur

ati

on

of

OUT

n(

n

=1,

4,

3

,7)

ET

H

MU

Xpl

eas

e

re

fer

to

Tabl

e2

5-

27.

Div

ide

r

OU

T1

MU

X

OUT

4

OU

T4

MU

X

Di

vi

de

r

OUT

3

10

(E

T

H

+

nonE

T

H

)

(E

T

H

+

nonE

T

H

)

(E

T

H

+

nonE

T

H

)

(n

on

ETH)

(nonET

H

)

ET

H

+

nonE

T

H

nonE

T

H

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDTCSPT857DNLG8

IC PLL CLK DVR SDRAM 40-VFQFPN

IDTCV105EPVG8

IC CLK GEN DESKTOP PC 48-SSOP

IDTCV110NPVG

IC FLEXPC CLK PROGR P4 56-SSOP

IDTCV115-2PVG

IC FLEXPC CLK PROGR P4 56-TSSOP

IDTCV115FPVG

IC FLEXPC CLK PROGR P4 56-SSOP

IDTCV119EPVG8

IC CLK GEN DESKTOP PC 48-SSOP

IDTCV133PAG

IC FLEXPC CLK PROGR P4 56-TSSOP

IDTCV136PAG

IC FLEXPC CLK ATI RS400 56-TSSOP

相关代理商/技术参数

IDT82V3358EDG8

制造商:Integrated Device Technology Inc 功能描述:IC PLL WAN SYNC ETHERNET 64TQFP

IDT82V3380

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SYNCHRONOUS ETHERNET WAN PLL

IDT82V3380A

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SYNCHRONOUS ETHERNET IDT WAN PLL?

IDT82V3380AEQGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SYNCHRONOUS ETHERNET IDT WAN PLL?

IDT82V3380APFGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:SYNCHRONOUS ETHERNET IDT WAN PLL?

IDT82V3380DQG

功能描述:IC PLL WAN SYNC ETH 100-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3380DQG8

功能描述:IC PLL WAN SYNC ETH 100-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3380EQG

功能描述:IC PLL WAN SYNC ETHERNET 100TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT